راه حل دو مرحلهای توصیف شده چالشهایی را برای طراحان نیز به همراه دارد که دستیابی به بازدهی بسیار بالا برای ال ای دی درایو یکی از آنهاست. این را می توان با یک مثال ساده نشان داد. اگر مرحله اول به بازدهی 92٪ دست یابد که برای مبدل فلای بک مقدار بسیار خوبی است و مبدل باک 97٪ بهره وری داشته باشد، بازده کلی سیستم کمی بالاتر از 89٪ خواهد بود. با در نظر گرفتن دستورالعمل آینده اتحادیه اروپا برای محصولات روشنایی، آیین نامه نورپردازی (SLR)، که جایگزین چندین مقررات قبلی خواهد شد و بازدهی حداقل 85٪ را برای یک درایور 50 وات می طلبد ، به نظر می رسد حاشیه مطلوبی وجود خواهد داشت. با این وجود بسیاری از تولیدکنندگان درایور ، بازده بالاتر را مهم تلقی می کنند ، خصوصاً از آنجایی که منجر به کاهش خنک کننده در یک محیط غالباً گرمایی می شود. در نتیجه، آنها استانداردهای خاص خود را دارند از جمله حداقل راندمان 88 درصدی ، مقداری که اغلب در توصیفات محصول به گوش می رسد. لازم به تأکید است که این سطح بازده در یک محدوده توان گسترده مورد نیاز می باشد ، نه فقط در حداکثر بار.

یک دسته اقدامات شناخته شده برای افزایش بازده هر دو مرحله وجود دارد. اما همه این اقدامات بطور قابل توجهی پیچیدگی و هزینه محصول را افزایش می دهد. یک راه حل ساده برای افزایش کارایی وجود دارد. این راه حل به سادگی از آرایش تغییر یافته مدار فیدبک تشکیل می شود . با این ترتیب جدید ، ولتاژ خروجی فلای بک متغیر می شود در حالی که اختلاف بین فلای بک و ولتاژ خروجی LED تنظیم خواهد شد.

افزایش بازده مبدل باک هیسترزیس ال ای دی درایو

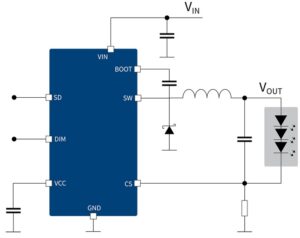

نکته ای که قابل ذکر است این است که مبدل باک هیسترزیس یک راه حل تقریباً مناسب برای مرحله دوم یک درایور LED است. بررسی عمیق تری در مورد مبدل باک هیسترزیس در اپلیکیشن نوت ILD8150 80 V یک مدار مجتمع LED درایور با کاهش هیبرید ارائه شده است. جزئیات بیشتر تئوری عملکرد مبدل های باک هیستریتیک برای خوانندگان علاقه مند به راحتی در دسترس است.

Figure 2: Schematic of hysteretic buck with ILD8150

اصل عملکرد آن کاملاً مناسب برای تأمین جریان خروجی ثابت است زیرا نیاز به هیچ حلقه فیدبکی برای تثبیت جریان خروجی وجود ندارد. بدون حلقه بازخورد به این معنی است که هیچ حلقه جبرانی لازم نخواهد بود. در نتیجه ، باک هیسترتیک در تمام شرایط ورودی و خروجی نرمال ، بدون قید و شرط پایدار خواهد بود. سرانجام ، همانطور که شماتیک شکل 2 به وضوح نشان می دهد ، تعداد اجزای مدار کاهش پیدا کرده است ، مخصوصاً MOSFET یکپارچه شده است. نکته کلیدی برای درک ایده بهبود بهره وری پیشنهادی این واقعیت است که باک هیستریتیک با فرکانس سوئیچینگ متغیر fS کار می کند. این فرکانس سوئیچینگ با توجه به مقدار سلف L ، دامنه ریپل جریان i و در نهایت ، ولتاژ ورودی و خروجی VIN و VOUT تعیین می شود.

چرا فرکانس سوئیچینگ fS اینقدر مهم است؟ صرفاً به این دلیل که بر تلفات ناشی از مدار باک هیستریتیک و به نوبه خود بر بازده احاطه دارد. تلفات هدایتی کل (به عنوان مثال مجموع تلفات هدایتی MOSFET و دیود) توسط مقاومت مربوطه و جریان LED مشخص می شود. از طرف دیگر ، تلفات کلید زنی به مقدار VIN و همچنین fS وابسته است.

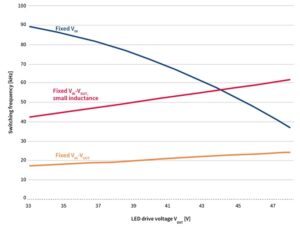

با توجه به تحلیل های موجود در منابع ، اختلاف پتانسیل( VIN – VOUT )بین ولتاژ ورودی و خروجی مقدار غالب در فرمول مربوط به fS است و اگر اختلاف VIN-VOUT ثابت بماند ، همانطور که در شکل 3 نشان داده شده است ، تغییر دومی بسیار کمتر خواهد بود.

با یک VIN ثابت (منحنی آبی) ، فرکانس با افت ولتاژ LED به سرعت افزایش می یابد و با کاهش یک سوم ولتاژ خروجی ، تقریباً سه برابر می شود. در نتیجه ، نه تنها تلفات کلیدزنی مبدل باک با دخالت یک عامل تقریباً سه برابر افزایش می یابد ، بلکه تلفات در سلف نیز به وسیله همان عامل افزایش می یابد. آنچه منحنی ثابت VIN (منحنی آبی) نشان می دهد این است که انتخاب یک سلف مناسب کار ساده ای نیست. مقدار سلف باید به اندازه کافی کوچک باشد تا تحت هر شرایطی فرکانس سوئیچینگ را از حد فرکانس شنوایی بالاتر نگه دارد ، اما برای محدود کردن تلفات نباید اجازه دهد مقدار فرکانس fS بیش از حد بالا برود. فرکانس های کلیدزنی بالاتر از 150 کیلوهرتز ممکن است باعث ایجاد مشکلات EMI نیز شوند.

وقتی اختلاف VIN-VOUT ثابت نگه داشته شود (منحنی زرد) ، رفتار کاملاً تغییر می کند. فرکانس به طور خطی با ولتاژ LED کاهش می یابد. این بدان معناست که می توان سلف مدار را به میزان قابل توجهی کاهش داد (مثلاً به نصف کاهش داد) ، در حالی که در اکثر دامنه عملکرد مدار ، فرکانس کلیدزنی مقدار پایینی دارد. در این حالت اندازه سلف ثابت نگه داشته می شود ، کاهش اندازه سلف به معنی تعداد دور های سیم پیچس کمتر و نیز تلفات کمتر است. اما ممکن است استفاده از اندازه و مقدار سلف کوچکتر برای یک طراح جذابیت بیشتری داشته باشد. منحنی قرمز در شکل 3 با مقدار سلف 2.5 برابر کمتر (340 میکرومتر) از آنچه در مورد دو منحنی دیگر (860 میکرومتر) است ، محاسبه شده است. این فرضیات به فرکانسهای نسبتاً متوسط منجر می شود ( همه در این حالت زیر 85 کیلوهرتز) ، که بسیار بعید است باعث ایجاد مشکلات EMI شود. می توانیم انتظار داشته باشیم که راندمان در بیشتر قسمتهای دامنه بار بهبود زیادی یابد و کاهش اندازه سلف منجر به طراحی فشرده تر و هزینه کمتر شود.

Figure 3: Variation of switching frequency vs. VOUT of a hysteretic buck with fixed VIN (blue), fixed VIN-VOUT (yellow), and fixed VIN-VOUT plus 2.5 times lower inductance(red)

دستهها

- اخبار (۱۲)

- بزرگراه (۱)

- پروژکتور (۱)

- خیابان (۱)

- دستهبندی نشده (۲)

- محصولات (۵)

- معابر محلی (۱)

- مقالات (۴۹)