در این مقاله ، دکتر ویریچ از Infineon Technologies ، یک روش ساده برای افزایش بازده ال ای دی درایور ها را توصیف می کند که می توانند با LED های با طیف گسترده ای از سطح جریان و توان کار کنند. علاوه بر این ، این روش امکان استفاده از سلف های کوچکتر در مرحله کاهنده مبدل را فراهم می کند ، که منجر به کاهش هزینه محصول کاهش سایز مبدل می شود.

ساختار کلی مبدل های دو مرحله ای

ساختار کلی مبدل های دو مرحله ای

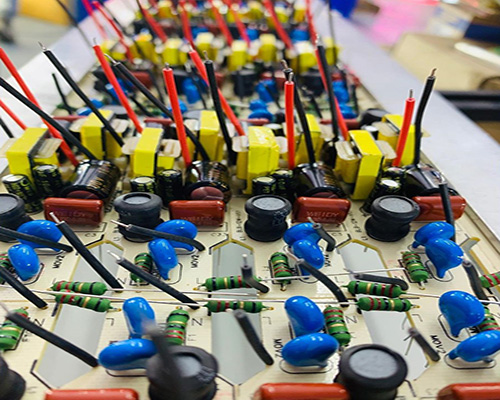

درایورهای LED مبتنی بر توپولوژی دو مرحله ای به دلیل عملکرد فوق العاده در قبال کیفیت توان ورودی ، دامنه دیمینگ بالا و کیفیت بسیار مطلوب ، به طور وسیعی مورد توجه قرار می گیرند. برای سطوح توان تا حدود 50 وات ، ترکیب مبدل فلای بک PFC و مبدل باک خروجی جریان ثابت به عنوان مرحله دوم بسیار محبوب است. چنین رویکردی امکان بهینه سازی تقریباً همه جنبه های سیستم را می دهد زیرا این ترکیب باعث افزایش آزادی طراحی در مقایسه با یک درایور یک مرحله ای می شود. با این حال ، دستیابی به بازده بسیار بالا می تواند برای توپولوژی های دو مرحله ای مسئله چالش برانگیزی باشد. روش ارائه شده در این مقاله بدون هیچ گونه هزینه اضافی و پیچیدگی طراحی ، راندمان بالاتری را به ارمغان می آورد. علاوه بر این ، امکان استفاده از مقدار و اندازه سلف کوچکتر در مبدل باک فرآهم می آید ، که منجر به طراحی های جمع و جورتر می شود.

درایورهای LED و کیفیت نور

کیفیت نور ، اول از همه ، به معنای عدم وجود هرگونه مصنوعات روشنایی است ، به عنوان مثال. اثرات سوسو زدن و استروبوسکوپی. هر دو در اثر پالس سازی جریان LED ایجاد می شوند و باید تا حد ممکن کم باشند. این بدان معنی است که هدف طراحی برای کیفیت خوب نور ، یک جریان خروجی است که تحت هر شرایط عملیاتی تا حد ممکن به DC خالص نزدیک باشد. هرگونه پالس ایجاد شده توسط یک جز AC در خروجی درایور با اثر منفی بر روی نور خروجی قابل تشخیص است. در حال حاضر ، هیچ استاندارد اجباری برای چنین مصنوعات نورپردازی وجود ندارد ، اما حداکثر سطح مدولاسیون نور ارائه شده در IEE1789-2015 یک راهنمای منطقی است.

دومین جنبه مهم وقتی درایور دیم می شود ظاهر می شود. در این حالت ، کمترین میزان کدیمینگ یک شاخص عملکرد مهم است و انطباق این سطح بین درایورهای مختلف مهم است. به عبارت دیگر ، کمترین سطح رشنایی باید بسیار دقیق باشد. آنچه بسیار مهم است عدم وجود مصنوعات ناشی از این شرایط توان خروجی کم است. سطوح کم نور اغلب توسط جریانهای LED ناپیوسته با استفاده از مدولاسیون PWM یا با رفتن به حالت ناپیوسته در مرحله خروجی اجرا می شوند. هر دو باعث پالسی سازی نور می شوند و ممکن است کیفیت نور را کاهش دهند.

حال بیایید الزامات مربوط به سمت ورودی ال ای دی درایور را در نظر بگیریم. استانداردهای بین المللی مانند IEC 61000-3-2:2014 ضریب توان بالا (PF) و محتوای هارمونیک کم (THD) جریان ورودی را می طلبد. اساساً ، این بدان معنی است که جریان ورودی دقیقاً با ولتاژ ورودی هم فاز است و یک شکل موج دقیقاً مطابق دارد ، یعنی هیچ اعوجاج و ناخالصی وجود ندارد ، نسخه 2018 استاندارد فوق الذکر ، برای سطوح توان ورودی بالاتر از 5 W کاربرد دارد و با جزئیات بیشتری نسبت به قبل ، به درایورهای قابل تنظیم توان می پردازد. به طور خلاصه ، به نظر می رسد تنظیم به کیفیت توان ورودی با یک مبدل تنظیم پذیر توان بسیار دشوار است.

در نتیجه ، درایورهای تک مرحله ای در این زمینه محبوبیت کمتری دارند و به طور فزاینده ای با راه حل های دو مرحله ای جایگزین می شوند. آنها بهینه سازی مرحله اول برای کیفیت عالی توان در محدوده وسیعی از توان خروجی را بسیار ساده تر می کنند. سپس مرحله دوم با ولتاژ DC منطقی پایدار تغذیه می شود و می توان برای تأمین جریان تغذیه تمیز و پایدار برای LED ها ، بهینه سازی کرد.

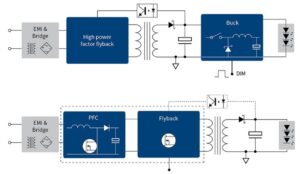

همانطور که در شکل 1 نشان داده شده است ، دو پیکربندی اساسی برای درایورهای دو مرحله ای وجود دارد: ایزولاسیون گالوانیک پس از مرحله اول یا بعد از مرحله دوم. بدیهی است که پیکربندی دوم برای برنامه هایی که بیش از یک کانال خروجی می طلبند ، به عنوان مثال ، سفید های تنظیم پذیر یا RGB ها مناسب نیست. همچنین ممکن است در برخی از طرح های با کانال خروجی منفرد در راه حل دوم ، که رابط دیمینگ از لاین توان جدا نشده است ، یک ضرر باشد. همه اینها کاملاً مستقل از این است که از تنظیم اولیه (PSR) یا طرف ثانویه (SSR) استفاده شود.

می توان نتیجه گرفت که درایورهای LED دو مرحله ای بر اساس یک PFC ایزوله شده و به دنبال آن مرحله باک ، همه کاره ترین راه حل برای میزان قدرت تا حدود 50 وات و بالاتر هستند. این معلوم میکند که چرا این توپولوژی برای درایورهای LED با نور بالا و کیفیت بالا بسیار محبوب شده است.

بازده سیستم

راه حل دو مرحله ای توصیف شده چالش هایی را برای طراحان نیز به همراه دارد. دستیابی به بازدهی بسیار بالا یکی از آنهاست. این را می توان با یک مثال ساده نشان داد. اگر مرحله اول به بازدهی 92٪ دست یابد که برای مبدل فلای بک مقدار بسیار خوبی است و مبدل باک 97٪ بهره وری داشته باشه ، بازده کلی سیستم کمی بالاتر از 89٪ خواهد بود. با در نظر گرفتن دستورالعمل آینده اتحادیه اروپا برای محصولات روشنایی ، آیین نامه نورپردازی (SLR) ، که جایگزین چندین مقررات قبلی خواهد شد و بازدهی حداقل 85٪ را برای یک درایور 50 وات می طلبد ، به نظر می رسد حاشیه مطلوبی وجود خواهد داشت. با این وجود بسیاری از تولیدکنندگان درایور ، بازده بالاتر را مهم تلقی می کنند ، خصوصاً از آنجایی که منجر به کاهش خنک کننده در یک محیط غالباً گرمایی می شود. در نتیجه ، آنها استانداردهای خاص خود را دارند از جمله حداقل راندمان 88 درصدی ، مقداری که اغلب در توصیفات محصول به گوش می رسد. لازم به تأکید است که این سطح بازده در یک محدوده توان گسترده مورد نیاز می باشد ، نه فقط در حداکثر بار.

یک دسته اقدامات شناخته شده برای افزایش بازده هر دو مرحله وجود دارد. اما همه این اقدامات بطور قابل توجهی پیچیدگی و هزینه محصول را افزایش می دهد. یک راه حل ساده برای افزایش کارایی وجود دارد. این راه حل به سادگی از آرایش تغییر یافته مدار فیدبک تشکیل می شود . با این ترتیب جدید ، ولتاژ خروجی فلای بک متغیر می شود در حالی که اختلاف بین فلای بک و ولتاژ خروجی LED تنظیم خواهد شد.

افزایش بازده مبدل باک هیسترزیس

نکته ای که قابل ذکر است این است که مبدل باک هیسترزیس یک راه حل تقریباً مناسب برای مرحله دوم یک درایور LED است. بررسی عمیق تری در مورد مبدل باک هیسترزیس در اپلیکیشن نوت ILD8150 80 V یک مدار مجتمع LED درایور با کاهش هیبرید ارائه شده است. جزئیات بیشتر تئوری عملکرد مبدل های باک هیستریتیک برای خوانندگان علاقه مند به راحتی در دسترس است.

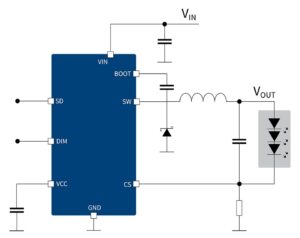

Figure 2: Schematic of hysteretic buck with ILD8150

Figure 2: Schematic of hysteretic buck with ILD8150

اصل عملکرد آن کاملاً مناسب برای تأمین جریان خروجی ثابت است زیرا نیاز به هیچ حلقه فیدبکی برای تثبیت جریان خروجی وجود ندارد. بدون حلقه بازخورد به این معنی است که هیچ حلقه جبرانی لازم نخواهد بود. در نتیجه ، باک هیسترتیک در تمام شرایط ورودی و خروجی نرمال ، بدون قید و شرط پایدار خواهد بود. سرانجام ، همانطور که شماتیک شکل 2 به وضوح نشان می دهد ، تعداد اجزای مدار کاهش پیدا کرده است ، مخصوصاً MOSFET یکپارچه شده است.

نکته کلیدی برای درک ایده بهبود بهره وری پیشنهادی این واقعیت است که باک هیستریتیک با فرکانس سوئیچینگ متغیر fS کار می کند. این فرکانس سوئیچینگ با توجه به مقدار سلف L ، دامنه ریپل جریان i و در نهایت ، ولتاژ ورودی و خروجی VIN و VOUT تعیین می شود.

چرا فرکانس سوئیچینگ fS اینقدر مهم است؟ صرفاً به این دلیل که بر تلفات ناشی از مدار باک هیستریتیک و به نوبه خود بر بازده احاطه دارد. تلفات هدایتی کل (به عنوان مثال مجموع تلفات هدایتی MOSFET و دیود) توسط مقاومت مربوطه و جریان LED مشخص می شود. از طرف دیگر ، تلفات کلید زنی به مقدار VIN و همچنین fS وابسته است.

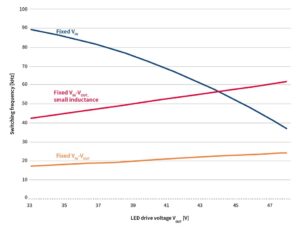

با توجه به تحلیل های موجود در منابع ، اختلاف پتانسیل ( VIN – VOUT )بین ولتاژ ورودی و خروجی مقدار غالب در فرمول مربوط به fS است و اگر اختلاف VIN-VOUT ثابت بماند ، همانطور که در شکل 3 نشان داده شده است ، تغییر دومی بسیار کمتر خواهد بود.

با یک VIN ثابت (منحنی آبی) ، فرکانس با افت ولتاژ LED به سرعت افزایش می یابد و با کاهش یک سوم ولتاژ خروجی ، تقریباً سه برابر می شود. در نتیجه ، نه تنها تلفات کلیدزنی مبدل باک با دخالت یک عامل تقریباً سه برابر افزایش می یابد ، بلکه تلفات در سلف نیز به وسیله همان عامل افزایش می یابد. آنچه منحنی ثابت VIN (منحنی آبی) نشان می دهد این است که انتخاب یک سلف مناسب کار ساده ای نیست. مقدار سلف باید به اندازه کافی کوچک باشد تا تحت هر شرایطی فرکانس سوئیچینگ را از حد فرکانس شنوایی بالاتر نگه دارد ، اما برای محدود کردن تلفات نباید اجازه دهد مقدار فرکانس fS بیش از حد بالا برود. فرکانس های کلیدزنی بالاتر از 150 کیلوهرتز ممکن است باعث ایجاد مشکلات EMI نیز شوند.

وقتی اختلاف VIN-VOUT ثابت نگه داشته شود (منحنی زرد) ، رفتار کاملاً تغییر می کند. فرکانس به طور خطی با ولتاژ LED کاهش می یابد. این بدان معناست که می توان سلف مدار را به میزان قابل توجهی کاهش داد (مثلاً به نصف کاهش داد) ، در حالی که در اکثر دامنه عملکرد مدار ، فرکانس کلیدزنی مقدار پایینی دارد. در این حالت اندازه سلف ثابت نگه داشته می شود ، کاهش اندازه سلف به معنی تعداد دور های سیم پیچس کمتر و نیز تلفات کمتر است. اما ممکن است استفاده از اندازه و مقدار سلف کوچکتر برای یک طراح جذابیت بیشتری داشته باشد. منحنی قرمز در شکل 3 با مقدار سلف 2.5 برابر کمتر (340 میکرومتر) از آنچه در مورد دو منحنی دیگر (860 میکرومتر) است ، محاسبه شده است. این فرضیات به فرکانسهای نسبتاً متوسط منجر می شود ( همه در این حالت زیر 85 کیلوهرتز) ، که بسیار بعید است باعث ایجاد مشکلات EMI شود. می توانیم انتظار داشته باشیم که راندمان در بیشتر قسمتهای دامنه بار بهبود زیادی یابد و کاهش اندازه سلف منجر به طراحی فشرده تر و هزینه کمتر شود.

Figure 3: Variation of switching frequency vs. VOUT of a hysteretic buck with fixed VIN (blue), fixed VIN-VOUT (yellow), and fixed VIN-VOUT plus 2.5 times lower inductance(red)

Figure 3: Variation of switching frequency vs. VOUT of a hysteretic buck with fixed VIN (blue), fixed VIN-VOUT (yellow), and fixed VIN-VOUT plus 2.5 times lower inductance(red)

پیاده سازی

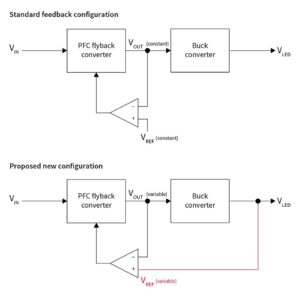

اجرای مفهوم توسعه یافته بسیار ساده است. به جای تثبیت ولتاژ خروجی مرحله فلای بک ، همانطور که در شکل 4 (بالا) نشان داده شده است ، اختلاف ولتاژ ورودی و خروجی باک به مقدار ثابت مثلا 5 ولت تنظیم می شود (شکل 4 – پایین). این مقررات عمدتا به بازسازی شبکه فیدبک نیاز دارد تا تقریباً به هیچ جز اضافی به غیر از مقاومت های کم هزینه نیازی نباشد.

Figure 4: Standard feedback configuration and proposed new configuration

تحلیل نظری گسترده ای انجام شده است تا ثابت شود چنین تنظیمات فیدبکی مشکلی برای پایداری حلقه کنترل ایجاد نمی کند. برای هر دو ، مبدل فلای بک PFC و باک هسترتیک ، توابع انتقال سیگنال کوچک تعیین شده و تجزیه و تحلیل پایداری حلقه با استفاده از MATLAB / SIMULINK اجرا شده است. همانطور که انتظار می رفت ، متوجه شدیم که این نوع بازخورد به جز موارد شناخته شده از یک مدار رایج ، هیچ مسئله پایداری ایجاد نمی کند. پاسخ حلقه باید آهسته باشد و پهنای باند حلقه مانند هر مبدل بازگشتی(فلای بک) PFC دیگری باید زیر 20 هرتز باشد. در عین حال ، این پیکربندی فیدبک هیچ تأثیر منفی بر عملکرد باک ایجاد نمی کند. همچنین لازم به ذکر است که نه روی برش ریپل و نه پاسخ بار تأثیر منفی نمی گذارد.

اینکه چقدر تفاوت در VIN-VOUT می تواند ایجاد شود ، یک سوال مهم برای بسیاری از طراحان است. این موضوع با حداکثر چرخه کار باک تعیین می شود.

در CCM ( مود هدایت پیوسته )، چرخه کار d همیشه برابر است با:

d = VOUT/VIN Thus VIN = VOUT, Max/ dMax

این در نهایت منجر به معادله می شود:

VIN-VOUT ≥ VOUT, Max (1/dMax-1)

ILD8150 حداکثر چرخه کار dMax 0.97 دارد. اگر حداکثر ولتاژ خروجی انتخاب شده باشد( 60 ولت ) ، حداقل اختلاف VIN-VOUT می تواند به اندازه 2 ولت باشد و منجر به سلفهای فوق العاده کوچک شود.

نتایج و جمع بندی

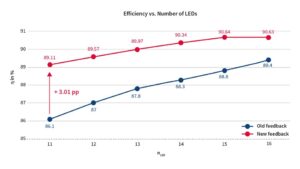

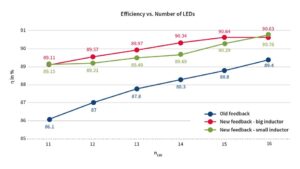

بهبود بهره وری مورد انتظار در سیستمی متشکل از مبدل AC-DC مبتنی بر XDPL8218 و به دنبال آن جفتک رحمی مبتنی بر ILD8150 تأیید شده است. در اولین آزمایش های راه حل پیشنهادی ، فقط پیکربندی فیدبک تغییر کرده است ، دقیقاً همانطور که در بالا توضیح داده شد. هیچ چیز دیگری برای این اعتبار سنجی اول تغییر نکرده است. بازده سیستم و افزایش آن با تغییر در مدار بازخورد در شکل 5 نشان داده شده است. در حالیکه در حداکثر ولتاژ خروجی (16 LED ≈ 48 V) ، افزایش بازده 1.3٪ است و در ولتاژهای خروجی پایین تر (11 LED ≈ 33 V) به بیش از 3٪ می رسد. حتی نتایج شکل 6 که نشان داده شده است هیجان انگیزتر است. در اینجا ما سلف خروجی باک را تغییر دادیم – یک دستگاه سلف نسبتاً بزرگ 860 میکروهانری با یک سلف 100 میکرو هانری جایگزین شد. اگرچه دومی دارای تقریباً پنج برابر حجم کم (1.4 سانتی مترمربع در مقابل 6.4 سانتی متر مربع) و یک عامل مشابه در وزن (7 گرم در مقابل 32 گرم) است ، اما بازده تقریباً یکسان می باشد.

Figure 5: Increase of system efficiency by changing the feedback configuration vs. output voltage

Figure 6: Comparison of system efficiency with altered feedback configuration and original 860 µH inductor (red) vs. 100 µH SMD inductor (green)

این یک نتیجه چشمگیر است زیرا افزایش بازده در حالی امکان پذیر است که همزمان حجم ، وزن و هزینه کاهش می یابد.

صفحه مرجع مطلب:

https://www.led-professional.com/resources-1/articles/how-to-increase-the-efficiency-of-two-stage-drivers

References:

[1] IEEE Recommended Practices for Modulating Current in High-Brightness LEDs for Mitigating Health Risks to Viewers, IEEE Standard 1789-2015,Jun. 2015.

[2] ILD8150 80 V high side buck LED driver IC with hybrid dimming

[3] ILD8150 high-frequency operation

[4] Thomas Altmann, Efficiency Optimization, Size and Cost Reduction of a LED Driver, Master Thesis, Technische Universität München, 2019

[5] IEC 61000-3-2:2014 Electromagnetic compatibility (EMC) – Part 3-2: Limits – Limits for harmonic current emissions (equipment input current ≤ 16 A per phase), 4th edition, 2014

[6] IEC 61000-3-2:2018 Electromagnetic compatibility (EMC) – Part 3-2: Limits – Limits for harmonic current emissions (equipment input current ≤16 A per phase), 5th edition, 2018